失效分析(FA)是利用各种方法检测设备的失效位置和失效模式的技术。需要及时反馈有关这些故障的信息,以提高生产中设备的质量和可靠性。

开封(解封)/去层是整个FA程序中的关键技术之一。该技术用于去除钝化并揭示设备的底层以供后续检查。酸脱盖和等离子脱盖技术广泛用于脱封。使用硝酸和硫酸等溶液进行酸脱盖是一种有用的钝化去除技术,但有时会导致铜线和铝线等金属线腐蚀。使用干法蚀刻技术的等离子体脱盖工艺比酸性脱盖工艺慢,但这些工艺可以去除特定的材料层,并以高选择性揭示底层和金属线。本文主要对失效分析领域涉及芯片开封和去层的等离子技术进行简要介绍

|

我们知道,在芯片失效分析领域,常见的开封方式,一般包括机械开封、化学开封以及激光开封.(具体可参看:常见芯片开封技术及仪器简介)各种方式之间也各有不同的特点,但等离子开封因为其“慢工出细活”的特点,在高端芯片领域获得了 其原理是通过电场功率将反应气体离子化后与需要去除的材料接触并产生化学反应而挥发。总体上属于化学开封,也有同时采用化学和物理机制的。 优点是没有物理应力,精细化程度高,不攻击敏感材料,可到达细孔凹陷部位。 缺点是速度慢,价格昂贵。 该领域的专用设备供应商主要来自欧洲和美国。 |

|

|

|

集成电路的芯片制造过程是通过掩模、光刻、离子注入、气相沉积、电镀、化学机械研磨(CMP)、腐蚀等多达几十、上百道工序,在硅衬底表面生长出有着特定逻辑功能的物理图形,这些物理图形从材质上包括Al、Cu、Ti、TiN和W等金属材料,以及单晶Si和多晶Si、SiO2和Si3N4等非金属材料[1]。

集成电路在制造、试验和应用过程中不可避免地会因为制造工艺、测试和环境应力、用户使用、寿命损耗等各种因素发生失效[2]。失效分析工程师需要通过各种方法定位失效位置,查找失效原因,剖析失效机理,在失效分析过程中需要对失效的集成电路进行去层解剖分析。芯片去层制备是在了解集成电路芯片制造工艺的基础上,采用化学腐蚀、机械研磨、离子刻蚀等技术手段逐层去除芯片各物理层次结构的过程。

集成电路芯片的去层制备过程包括对表层玻璃钝化层的去除、金属化层的去除、阻挡层的去除、中间介质层的去除、底层多晶层的去除和有源区的制备。根据制造工艺和材料的差异,一般可以选用离子刻蚀、化学腐蚀和机械研磨等方法。目前反应离子刻蚀法(RIE)因为其独特的优势已被设备制造商和FA实验室广泛,目前市场上相应品牌的产品也相当成熟,如日本SAMCO,英国Oxford等.以目前在国内市占率较高的日本SAMCO为例:(代表机型10NR) |

|

1、可处理具有高选择性和高纵横比的各种材料

● Si(在埋入氧化物

● (BOX) 处的蚀刻停止)

● 氧化物

● 硼硅酸盐玻璃 (BSG)、磷硅酸盐玻璃 (PSG) 和硼磷硅酸盐玻璃 (BPSG)

● 蚀刻停止在块体 Si 处)

● 氮化物

● 金属间电介质 (IMD)

● 层间电介质 (ILD)

● 低介电

● 聚酰亚胺

● 环氧的

● 高分子薄膜

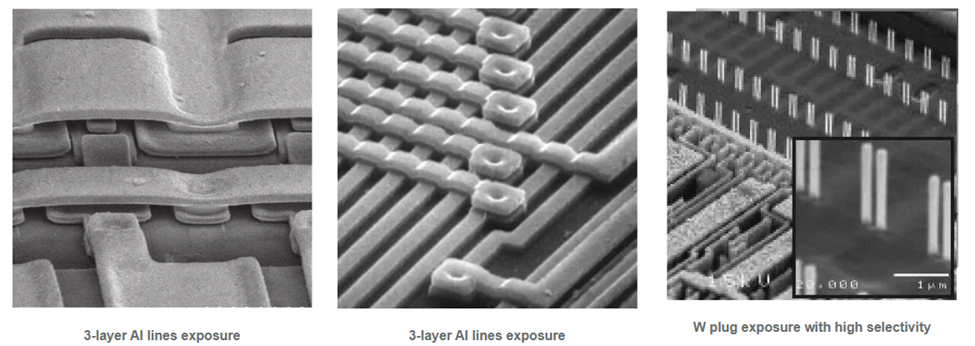

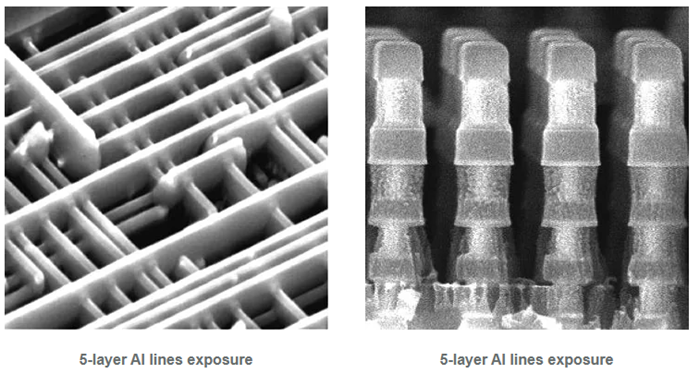

2、铝线成功暴露,没有分层和侵蚀。该技术能够对复杂结构的芯片进行逐层去钝化和故障检测。

3、System Lineup from Die to 300 mm for Plasma Decapsulation 适应最高到300mm的对象尺寸(4~12寸)

4、Endpoint Detection for Precise and Repeatable Etch Stop终点检测,实现精确且可重复的蚀刻停止

|

为了实现可靠的去钝化工艺,需要精确的蚀刻停止。Samco 提供用于去钝化的可选终点点检测系统。该系统能够对包括氧化物和氮化物在内的薄膜和透明薄膜进行精确的厚度监测。它可实现可重复的全自动处理。 |

|

上一篇: RIE反应离子刻蚀在半导体工业中的应用

下一篇: 无目镜光学技术助力人造钻石产业